# JTAG テストによる基板検査

# コスト削減と品質向上に役立つ10のヒント(後編)

アンドールシステムサポート(株)/谷口 正純、佐々木 陽助

# 1. はじめに

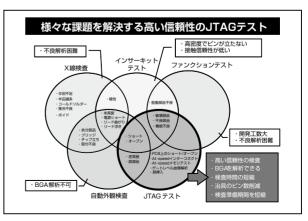

現在の厳しい価格競争に打ち勝つためには、開発コスト、生産ラインのコストダウンと製品の高い信頼性が求められる。多くの企業では、高密度実装基板の検査カバレッジを確保するために、様々な検査手法を組み合わせて検査内容を補完し合いながら基板の検査を行っている。複雑な基板を検査・解析するために、いくつかのストラクチュアルテスト手法が製造ラインで使用されている。

本誌先月号掲載の前編では、インサーキットテストとファンクションテストの課題とJTAGテストとの組み合わせによる検査カバレッジの拡大について紹介した。後編となる今回は、X線検査と自動外観検査の課題と解決策、またJTAGテストによるコスト効果を実際の導入企業の事例をもとに紹介する。

# 2.ヒント⑥ X線検査が抱える課題

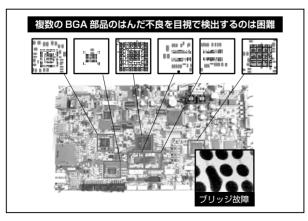

多くの企業では、BGA搭載基板の検査でX線検査を実施 している。X線検査装置には、XY平面の解析ウィンドウを

図1 技術者のスキルに影響されるX線検査

もつ2次元のX線検査(図1)とZ平面まで描写可能な3次元のX線検査の2つのシステムがある。多くの企業が採用している2次元のX線検査は、同図のブリッジ故障の画像のようなグレイスケールの画像が出力される。この画像からは、BGAの2つのボールがショート不良を起こしていることが分かる。

#### ●X線検査は技術者のスキルが必要

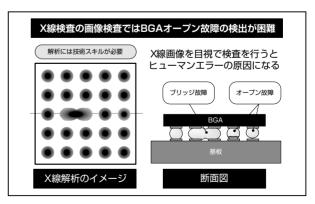

標準的なX線検査装置では、検査担当者が目視で画像をもとに不良個所を診断する必要がある。図2のようにブリッジ故障は目視検査で発見しやすいが、オープン故障は発見が困難であり、目視検査ははんだ不良を見逃してしまうなど、ヒューマンエラーの原因となってしまう。

X線検査は大規模の初期設備投資が必要であり、X線検査結果の画像の出力と目視検査に時間がかかってしまうため、通常、はんだ不良が考えられるターゲット基板のみに絞って適用されることが多い。

## ●全自動X線検査と3次元X線検査

接合部の100%の検査を望むのであれば、合格品の画像から自動で合否判定ができる全自動システムがある。全自

図2 X線検査によるBGA解析イメージ

動X線検査システムは、高い付加価値を持つ製品や高い品質を要求され、責任問題を明確にする必要があるような大量生産、少量生産混在の設備においても使用される。

また、BGAのオープン不良を検査するために、3次元でX線検査ができるものがある。断面図による検査能力をもち、はんだ接合部の面積や厚さを含むシングルサイドとダブルサイドの表面実装アセンブリを検査できる。しかし、いずれのX線検査の画像の解析も現実には主観的なものであり、熟練した技術者のスキルが要求される検査技術である。

#### ●JTAGテストで検査コストを削減する

X線検査によるはんだ品質の検査は、基板の品質を保証する上で重要である。しかし、価格競争が厳しい製品の生産ラインでは、検査コストを削減するために、量産基板の全数に対してX線検査は実施されていないことが多い。

量産する製品の品質を維持し、検査コストを削減するために、JTAGテストを導入する企業が増えている。JTAGテストは検査時間が短く、設備コストが大幅に安価になり、量産時の全数検査に適用できるようになる。さらに、JTAGテストは通電試験であり、検査技術者のスキルに影響されることなく、確実にはんだ不良を検出することができる。

JTAGテストを導入している企業では、JTAGテストを使い故障個所を特定した上で、不良基板をX線検査、3次元X線検査で故障解析を行うケースが多い。このようにして、量産時の検査コスト削減と製品の品質を向上することができる(表 1)。

#### 3. ヒント⑦ 自動外観検査が抱える課題

自動外観検査(AOI)はリフロー前、リフロー後の段階で部品の未実装や実装不良の検査をするための製造プロセスにおいて、何年も前から使用されているテスト手法である。 理想的にはリフロー後の自動外観検査は、製造ラインの不

| X 線検査の特徴                              |                                                 |

|---------------------------------------|-------------------------------------------------|

| 【テスト準備】<br>・技術者のスキルが要求される             | 【故障解析】 ・主に検査担当者の目視検査 ・BGA のブリッジ故障が分かる           |

| X 線検査が抱える課題                           |                                                 |

| 【被検査基板】 ・BGA のオープン不良特定が困難 ・検査範囲が限定される | 【テストの課題】 ・大規模な設備投資が必要 ・検査に時間がかかる ・電気的に通電を保証できない |

表1 X線検査の特徴と課題

良ゼロを実現できるスタティックなプロセス制御技術の一因となりうる。ただし、外観検査ははんだ接合部の表面部分の観察しかできないため、BGAパッケージなどの外観検査では見えないはんだ不良などの不具合は、X線やJTAGテストのようなテスト手法を用いないと検出することはできない。

自動外観検査は、正しい部品が実装されている基板の画像を基準として、検査対象の基板の画像とのグレイスケール相関により比較検査を行う。しかし、図3の検査画像のとおりに描写された背景色の場合、グレイスケール相関で問題が発生する可能性が高く、検査結果としてこの画像はエラーと判断されてしまうことが考えられる。

しかし、エレクトロニクス業界で要求される自動外観検査の検査スピードと画像の鮮明さの改善により、ベクターイメージング計測技術と呼ばれる新しいソリューションが現れた。これはハイスピードの量産ラインで、プリント基板の検査をより詳細に検査できる。ベクターイメージング計測技術は、形状位置の検索技術であり、グレイスケール画素の観察よりむしろ幾何学的特徴の抽出に基づいて計測される。したがって、幾何学的な特徴を使用するため、画像解析時の色の違いや製造誤差のようなサイズの非線形変化の影響を受けない(表2)。

図3 自動外観検査の検査画像

| 自動外観検査の特徴                                           |                                               |

|-----------------------------------------------------|-----------------------------------------------|

| 【テスト準備】<br>・サンブル基板を良品として登録                          | 【故障解析】<br>・誤部品、はんだ不良を検出できる<br>・検査者のスキルに影響されない |

| -<br>自動外観検査が抱える課題                                   |                                               |

| 【被検査基板】 ・BGA 部品を検査できない ・スルーホールを検査できない ・基板の内層を検査できない | 【テストの課題】 ・電気的な通電を保証できない ・目に見えない不良が分からない       |

表2 自動外観検査の特徴と課題

# 4.ヒント® 検査を補完するJTAGテスト

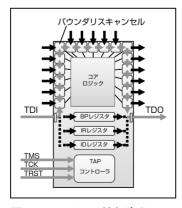

ストラクチュアルテスト手法において、BGA 搭載基板に対するピンによるアクセスの問題を解決するため、バウンダリスキャン方式のJTAGテストがIEEE1149.1として規格化された。その後、多くのシリコンベンダがIEEE1149.1に準拠したデバイスを数多く供給したため、JTAGテストは多くの企業に広まった。現在では、マイコン、FPGA、DSP、チップセットなど、非常に多くのバウンダリスキャン対応デバイスが供給され、世界中の生産ラインで日常的に基板検査とインシステムプログラミングのためにJTAGテストが使用されている。

#### ●JTAGテストに対応しているデバイス

JTAGテストに対応するデバイスは4本(オプションのリセット信号が含まれる場合は5本)のテストアクセスポート(TAP)と各ピンの内部にバウンダリスキャンセルが内蔵されている。また、JTAGテストを実行するために、バウンダリスキャン機能のレジスタとコアロジックとのマルチプレクス回路をもっている(図4)。シリコンベンダは、デバイスごとにバウンダリスキャンの内部ロジックを記述したBSDL(バウンダリスキャン記述言語)ファイルを提供している。このBSDLファイルは、デバイスベンダのホームページよりダウンロードできる。

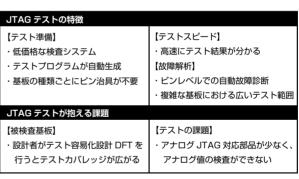

#### ●課題を解決するJTAGテスト

JTAGテストは、表3の特徴があり、様々な手法の検査と組み合わせて使用されている。図5は、現在のインサーキットテスト、X線検査、自動外観検査、ファンクションテストとJTAGテストのエレクトロニクスアセンブリ業界共通の

る。

図4 JTAG テスト対応デバイスの 内部

## 5. ヒント 9 JTAG テストの応用事例

JTAGテストを行うためには、バウンダリスキャン対応デバイスがボード上で使用されている必要がある。シリコンベンダの多くの主要デバイスには、バウンダリスキャンがすでに組み込まれているので問題はない。しかし、基板上には、バウンダリスキャン非対応のデバイスが多くあり、これらはJTAGテストでダイレクトに制御することはできないが、バウンダリスキャン対応のデバイスからアクセスすることにより検査できる。このように、テストカバレッジを上げるために、すべてのデバイスがバウンダリスキャンに対応している必要はない。

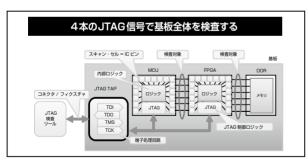

#### ●4本のJTAG信号で基板全体をテストする

基板上に1個でもバウンダリスキャン対応のデバイスがあれば、JTAGテストを実行できる。JTAGテストでは、DDRメモリなどのバウンダリスキャン非対応のデバイスをJTAG対応デバイスからコントロールすることにより、基板全体を検査することができる。また、多くの基

表3 JTAGテストの特徴と課題

図5 様々なテスト手法と製造不良のタイプ

板上には、マイコンをデバッグするためのJTAG ICE用インタフェース、PLDやFPGAを書き込むためのJTAGダウンロードケーブル用のインタフェースを備えているので、JTAGテスト用に特別な仕組みを用意する必要はない。JTAGテストのモードに切り替えられるように、BSDLファイルに記載されている端子処理をし、試作時にはコネクタを使ってJTAGテストを行い、量産時にはフィクスチャを使ってJTAGテストを実施している(図6)。

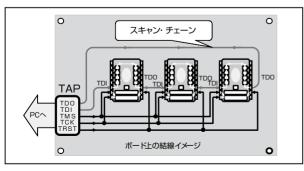

# ●シンプルなJTAGテストの回路

バウンダリスキャン対応デバイスはボード上に1つ、あるいは複数のチェーンで内部接続される。図7のように、JTAGテストは最初のデバイスのテストデータ出力ピン(TDO)と次のデバイスのテストデータ入力ピン(TDI)をシーケンシャルに接続して実行される。このシフト動作などを含むテスト命令を制御するため、基板上のバウンダリスキャン対応デバイスはテストクロック(TCK)とテストモードセレクト(TMS)信号が接続される。

これらの回路もJTAG ICEやJTAGダウンロードケーブル用の回路構成をそのまま活用できるため、検査用に特殊な回路は必要ない。JTAGテスト実行時には、PCにインストールされたJTAGテスト用のソフトウェア『JTAG ProVision』で自動生成されたテストプログラムが、JTAGコ

図6 基板全体をテストするJTAGテスト

図7 JTAGテストのイメージ

ントローラ(USB、イーサネット)から基板上のバウンダリス キャンデバイスをコントロールしてテストが実行される。

# ●短期間でテスト環境が整うJTAGテスト

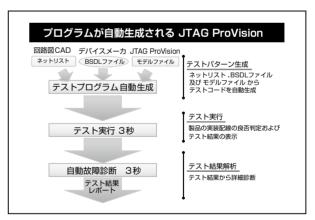

JTAGテストを使わずに、複雑な検査基板を検査するためには、生産技術者は数週間の時間をかけてテスト環境を構築している。しかし、JTAGテストによる量産試作基板のテストとデバッグは、数日から1週間ほどでデバッグまで完了できる。

業界標準のJTAGテストソフトウェア『JTAG ProVision』では、10万種類を超える部品モデルが用意されているため、基板のロジック機能を熟知する必要がなく、テストプログラムの生成から故障解析まで自動で行われる。したがって、ストラクチャード不良を摘出するための少量多品種のテストは製造要員でも可能である(図8)。

#### ●JTAGテストのテストカバレッジ

JTAGテストのテストプログラムが自動生成されると、 図9のように回路CAD上にJTAGテストのカバレッジが 色分けして表示される。ここでマーキングされない回路は、

図8 テストプログラムが自動生成されるJTAGテスト

図9 JTAG ProVisionのテストカバレッジ検証ツール

JTAGテストの範囲外になるため、従来の検査システムで 補完して検査範囲を拡大すればよい。

したがって、今までインサーキットテスト、ファンクションテストですべての回路をテストしている企業にとっては、JTAGテストでカバーしている範囲が広いほど、検査の準備時間を大幅に減少できることになる。JTAGテストはプログラムが自動生成されるため、設計者と検査担当者の作業コストを大きく削減できる。

## ●少量多品種でもコスト効果が得られるJTAGテスト

JTAGテストは、将来の高密度基板に対するインサーキットテストで予測されるピンアクセスの問題を克服するために開発された。JTAGテストは被検査基板へのアクセスが簡単であり、テスト準備の容易さ、テストツールが安価であり、テスト基板が変わっても同じツールが使えるため、試作基板や少量生産の製造不良に対しても効果を発揮する。図10のように、生産する機種ごとにテストシーケンスを作成し、試作の段階から量産まで同じテストシーケンスを使うことができる。検査担当者は1クリックですべてのテストが完了し、検査ログがHTML形式のファイルで自動保存される。

図10 量産工程で活用できるテストシーケンサ

#### インシステムプログラミングのメリット

- 1. プロトタイプ時には、書込み用のソフトウェア開発前に JTAG テストシステムからメモリにアクセスできる。

- 2. 1工程で製造不良の検査とメモリ、FPGA の書き込みができ、 オペレーションのコストを削減できる。

- 3. 生産ラインの中において、出荷プログラミングの削除と 最新のプログラムへの書き換え、プログラムのカスタマイズが できるようになり、在庫管理とハンドリングを簡略化できる。

表4 インシステムプログラミングのメリット

## ●インシステムプログラミングのメリット

JTAGテストシステムの拡張機能に、インシステムプログラミングの機能があり、基板上のフラッシュメモリ、シリアルメモリ、PLD、FPGAなどをJTAGテストシステムから書き込むことができる。

JTAG ProVisionでは、プログラミングするメモリの部品ライブラリを選択すると、自動的にメモリ制御用のプログラムが生成される。インシステムプログラミングには、表4の通り多くのメリットがある。

#### ●LSIのセルフテストBISTと基板テストのJTAG

主要FPGAベンダや専門シリコンベンダは、LSIのセルフテスト機能であるビルトインセルフテスト(BIST)機能をIPコアで提供している。設計者はこれらのテスト用のIPを組み込みシリコンの総合的なテストやゲートレベルの不良検出まで実現している。

JTAGテストシステムからビルトインセルフテスト (BIST) を実行できるため、LSIのセルフテストと基板上のはんだ不良、パターン不良まで、1つの検査工程でテストできる。その結果、生産ラインのオペレーションコストが削減でき、さらに製品基板の信頼性が高くなる(図11)。

# 6. ヒント⑩ 利益を生み出す JTAG テスト

JTAGテストによる様々な部門の利点は、企業に堅実な利益を導き出す。製造プロセスの改善により、結果として製品化までの期間の短縮、設備投資の削減、設備所有者のコスト軽減が実現できる。

#### ●製品化までの期間短縮

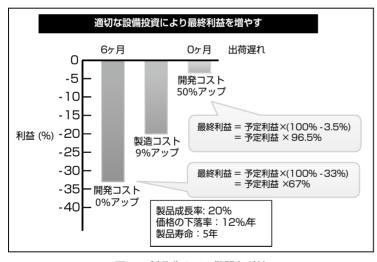

製品化までの期間短縮による利益面での重大な恩恵は、様々な研究の中で論文化されている。1つの調査結果では、平均して6ケ月製品出荷が遅れると、利益は33%のロスとなる。しかし、製品開発コストが50%アップしても、利益の減少はわずか3.5%になる。競合が多いマーケットにおいて、製品投入が早ければ早いほど、製品寿命は延び、その結果、投資に対するリターンが大きくなる(図12)。

## ●コンカレントエンジニアリング

企業経営者は、新しい製品を望ましい価格で、望ましい時間に、望ましい生産を行うために、コンカレントエンジニアリングを導入する責任がある。コンカレントエンジニアリングとは、設計から製造にいたる様々な業務を並列に行う

ことにより、大幅に開発期間を短縮する開発手法である。 理想的には、設計技術、製造技術、検査技術、マーケティング の代表からなるプロジェクトチームを作り、製造や他の機 能範囲の影響を受ける問題による再設計を避けるため、規 則的にミーティングを持つとよい。

JTAGテストとBISTを組み合わせるとLSI内部も検査できる 基板 検査対象が広がる MCU **FPGA** DOR ロジック ロジック JTAGテストシステム メモリ JTAG ProVision BIST BIST. **JTAG** TAP JTAG JTAG LSI内部も検査できる

図11 JTAGテストとBISTのイメージ

図12 製品化までの期間と利益

図13 従来手法の検査工程

結果として、設計者が費やしている余分な時間を短縮でき、重要なライフサイクルのコスト削減が実現される。もし、再設計が避けられないのであれば、不必要なコストを避けて、最新の製造プロセスに適合するような設計手法が採られる。

JTAGテストは、製品開発に対するコンカレントエンジニアリングのアプローチに最も適合しているテスト手法の1つである。テストエンジニアリングの効果は、製品の開発段階から製品寿命までテスト可能であることを保証できる。

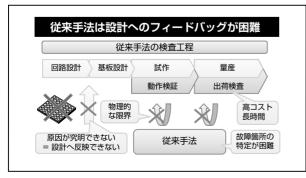

#### ●製品化までの期間を劇的に短縮できる

JTAGテストを導入したテスト容易化設計DFTにより、製品を検査するための複雑なファンクションテストのプログラム開発は不要になり、テストカバレッジの向上やピンレベルの故障診断が可能となる。さらに、ファンクションテストの長期間のデバッグ作業や無駄なリワークサイクルを避けるのに役立つ。図13の従来手法の検査工程では、BGAの故障個所の特定が困難であり、製品の開発・製造サイクルにフィードバッグすることが難しい。

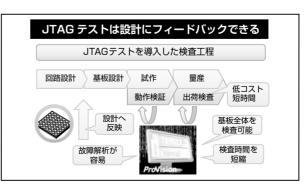

しかし、図14のJTAGテストを導入した検査工程では、製品の開発から生産までの様々な場面で検査結果をフィードバックできることが分かる。

これまでの国内導入実績と経験から、JTAG テストがテストカバレッジとテスト開発サイクルタイムを大きく改善でき、製品化までの 期間を劇的に短縮していることが分かる。

図14 JTAGテストを導入した検査工程

## ●試作基板をデバッグする期間を短縮する

試作基板のデバッグ時には、バグの要因として、はんだショート、オープン、パターン不良のような製造不良と設計ミスが混同している。しかし開発時においては、専用のテスト装置や特殊な検査治具への投資は、プロトタイプ段階の暫定的な性質があり、最小限に限られてしまう。結果として、試作基板のデバッグは、不良検出や故障診断が難しく、問題切り分けのために特殊なファンクションテストプログラムを開発して実施している。そのため、デバッグのためだけに開発者がプログラムを開発するなど、新製品を開発するためのリソースが浪費されている現状がある。

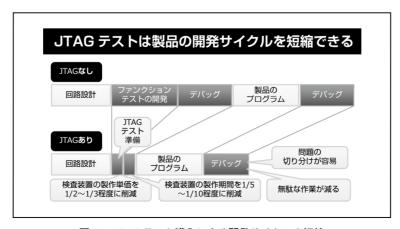

JTAGテストは、この状況を大幅に改善できる。設計者は、回路設計が終わるとすぐにJTAGテストの検査環境を手間がかからずに短時間で準備できるため、試作基板のデバッグ前にテストを実施して、物理的な不良を取り除くことができる。このメリットは、特にシステムが複雑で、試作基板を多数製作する大規模なシステムの設計に有効であり、製品実現化までの期間の目標達成に大いに貢献できる(図 15)。

#### ●JTAGテストによるコスト削減

工場における量産立上げ時のトラブルによる遅延は、新製品の決められたリリース日を遅らせる重要な問題である。トラブルの解決には、設計者の支援が必要になるが、それは少なくとも以下の2つの観点から能率的ではない。

- ①設計者の専用テスト環境は、量産ラインでのサポート には適さない

- ②設計者を製造のサポートに向けることは、製品開発の本来の役目に影響を与え、その結果として他の新製品

## のプロジェクトが遅延する

さらにそのような作業方法は、高い品質を保証できず、予算オーバーを導くことになる。これまで紹介したように、JTAGテストを適用することにより、試作基板が完成する前にテストプログラムが自動生成でき、設計者のデバッグ期間を大幅に削減できる。また、設計者が生成したテストプログラムは、そのまま生産ラインで利用できるため、生産技術者の負担は大幅に軽減でき、高い品質を保証できる(表5)。

#### ●確実に効果がでる設備投資

業界スタンダードのJTAGテストシステム『JTAG ProVison』は、回路CADから出力されるネットリストからJTAGテストパターンを自動生成し、自動的に故障解析することができる。また、故障個所は、プリント基板のレイアウトCAD上で示されるため、修理時間を短縮することができる。この設備投資は、設計サイクル、生産ラインに対して直接よい影響を与える。

JTAGテストの導入は、特に製品ライフサイクルの量産 段階で検査に対する投資をより削減することができる。コスト削減には3つの要因がある。

- ①JTAGテストシステムは従来のインサーキットテスタ より大幅に安価である

- ②高価な冶具が不要になり、テストできる基板の種類を 増やすことによりコストを軽減する

- ③故障解析の時間短縮により、テスタの台数を削減でき、 工場のテスタ ] 台あたりの稼働率が上がる。

図15 JTAGテスト導入による開発サイクルの短縮

# ●JTAGテストを活用するための技術レポート

当社が20年以上のJTAGテストの技術サポートを通じて得たノウハウと、JTAGテストためのテスト容易化設計DFTガイドラインを技術レポートとして無料で提供している(図16)。また、将来の3次元LSIのTSV技術、部品内蔵基板のテストに関する技術内容まで幅広く提供している。当社のホームページから無償で入手できる。

# 7.まとめ:『企業の成長に繋がるJTAG ProVision』

多くの企業では、量産検査の準備期間が大変短く、従来のファンクションテストやインサーキットテストでは、量産開始までに供給が間に合わない、もしくは生産の初期では十分なテストカバレッジが取れないまま生産されることが

ある。検査が不十分のため製品の品質は低下し、顧客の期待と企業のブランドネーム、そして保守・修理費用における デメリットの影響は、長い目でみた企業の成長に対し大き な損害を被ることになる。

JTAGテストでは、生産ラインの立ち上げ前にテストの準備が整うため、生産の初期の段階から高いテストカバレッジが保証される。また、設計者、生産技術者は、JTAGテストによりテスト準備の時間や故障解析の時間を削減でき、本来の開発、検査の業務に集中できる環境が整うため、新製品の品質は高いものになる。

このように、企業の未来を担う新製品の高い品質と信頼性を改善でき、顧客の期待に応えられるため、JTAGテスト手法の業界スタンダードである『JTAG ProVision』は企業の成長に繋がる。

# 製品開発サイクルを短縮する JTAG テスト『 JTAG ProVision 』

- 試作基板の物理的不良を無くし、デバッグが迅速に行える。

- 優れたパターン生成ツールの能力による開発期間の短縮できる。

- テストカバレッジを可視化でき、基板のレイアウトを最適化できる。

- インサーキットテスタ治具を削減し、生産ラインを迅速に立上げる。

- ピンレベルの自動故障診断により、修理時間を削減できる。

表5 JTAGテストによる製品開発サイクル短縮の効果

## JTAG テスト導入による利益 (お客様の事例より)

- テストプログラム準備時間 1カ月 → 1日

- テストデバッグ時間 10日間 → 5時間

- ピンカバレッジ40% → 95%

- 故障切り分け時間1 時間 → 5分

- テスト保守、サポート時間 30分/月→ 5分/月

- 試作基板のテストカバレッジは 90%あった。

- ピンレベルの自動故障診断により、修理時間を削減できた。

表6 JTAGテストによるお客様の利益

# JTAG 技術レポートで多くの事例とノウハウを提供 主な掲載内容 ● JTAG テストの基礎 ● BGA 実装と JTAG テスト ● JTAG テストとテスト容易化設計 ● 差動信号の JTAG テスト規格 ● 部品内蔵基板と TSV と JTAG テスト

図16 JTAGテストの技術レポート