はじめに

JTAGテストは、0.5mmピッチ以下の狭ピッチBGA実装基板に有効なテスト手法です。

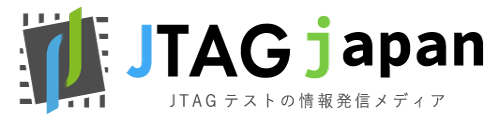

- JTAGテストは、高密度実装のテストクライシスを解決するために考案された新しいテスト手法です。(バウンダリ・スキャン・アーキテクチャ)

- このIEEE 1149.1規格をバウンダリスキャン又はJTAGと呼びます。

- JTAG (Joint Test Action Group) は、規格を推進したグループ名です。

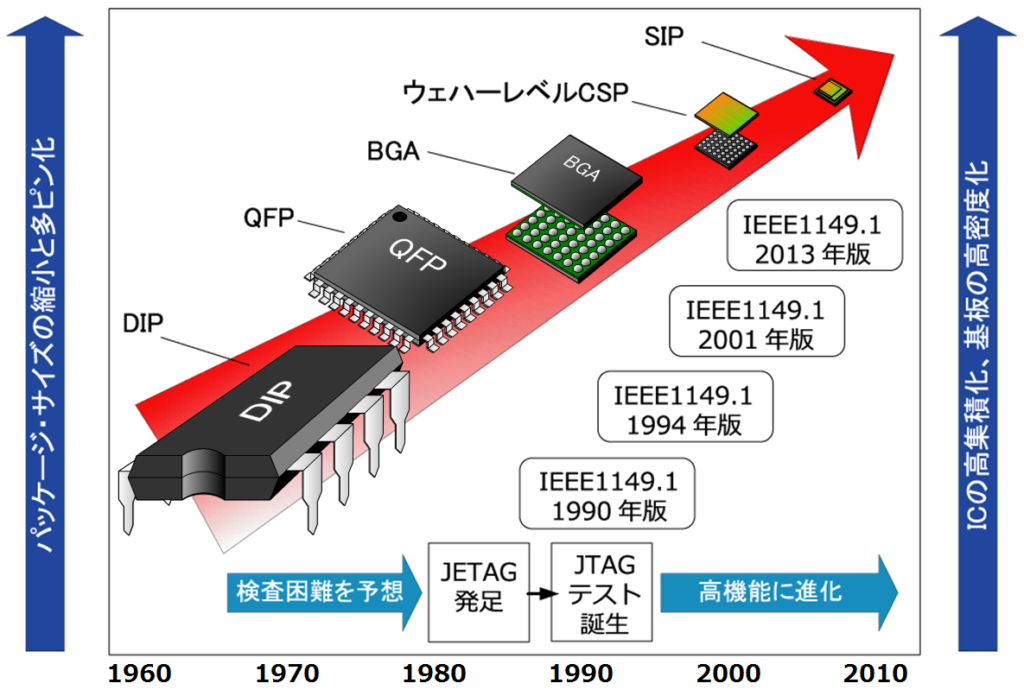

JTAG ProVisionがBGAデバイスが実装された基板に対する効果的な実装検査を実現します。

JTAGテストは何ができる?

ボードテストのさまざまな問題を効率よく解決・防止します。

- BGAを電気検査:BGA、狭ピッチQFP 実装基板の実装保証ができ、不良品の市場流出防⽌します

- テストパターンを自動生成:テストアプリケーションの⾃動⽣成により検査準備の⼯数を削減します

- 故障診断の自動化:正確な故障診断により製造不良の再発防止を実現できます

- テスト範囲の自動評価:テストカバレッジ評価ツールにより瞬時にカバレッジを確認できます

- オンボード書き込み:JTAG経由でフラッシュメモリ、PLDの書き込みができます

- 治具の簡素化:ピン治具で必要とされるプローブの本数を削減できます

- 廃棄基板の削減:JTAGテストは廃棄基板の削減により自然環境を保護します

JTAGテストはBGAパッケージや、CSPパッケージが実装された基板上で、端子がデバイスと基板の裏側に、隠れてしまうため、従来のプローブで端子を当たるICTや外観検査装置では実装不良を検出することができない場合でも、問題なく実装検査を実現できる手法です。

1

実装基板の合否判定

2

ネットレベルの故障解析

3

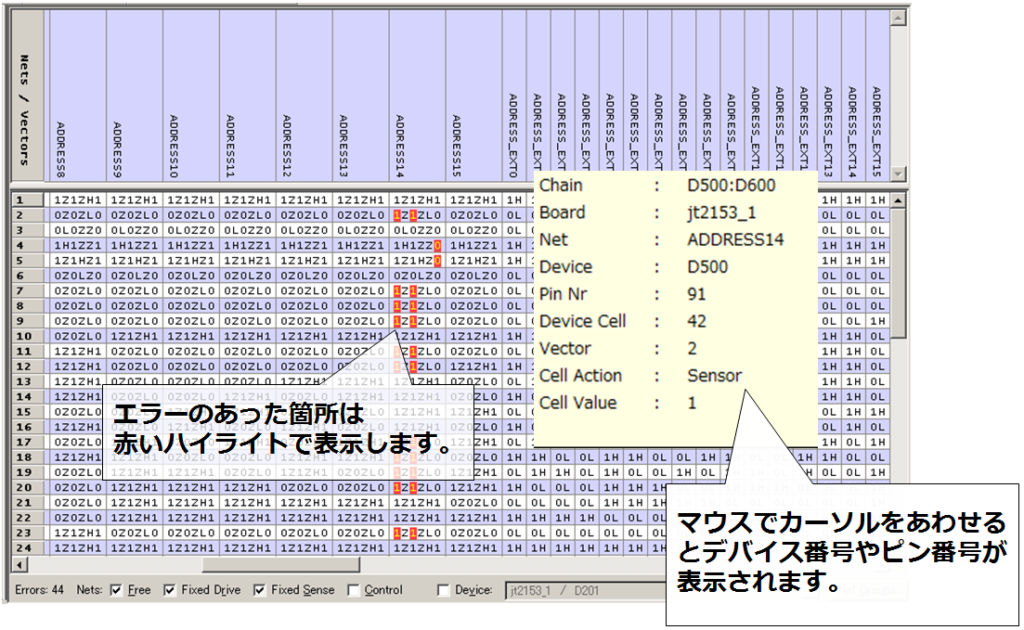

故障箇所の部品名及びピン番号の特定

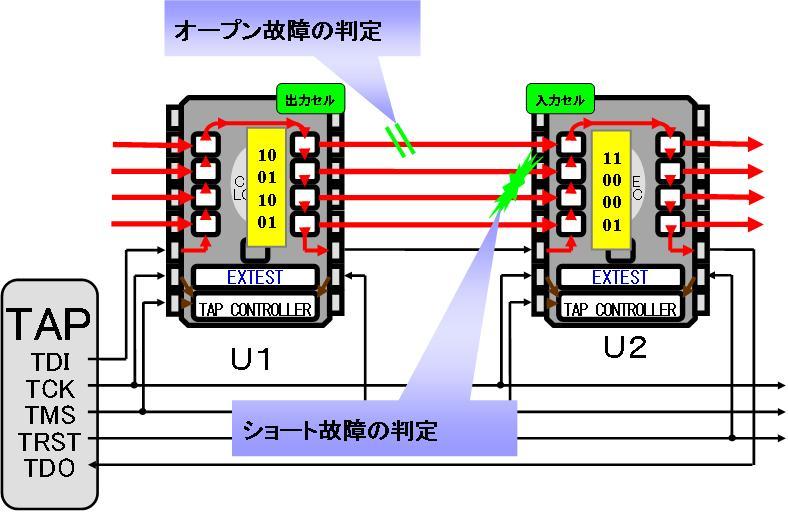

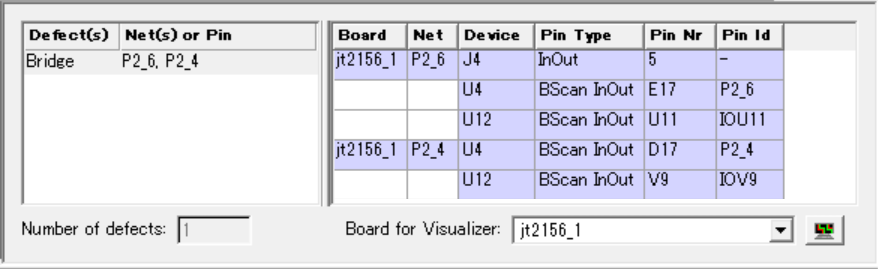

- ショート故障の診断結果

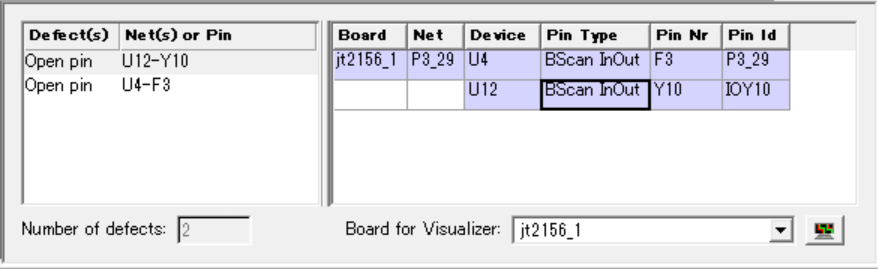

- オープン故障の診断結果

4

オンボードプログラミング

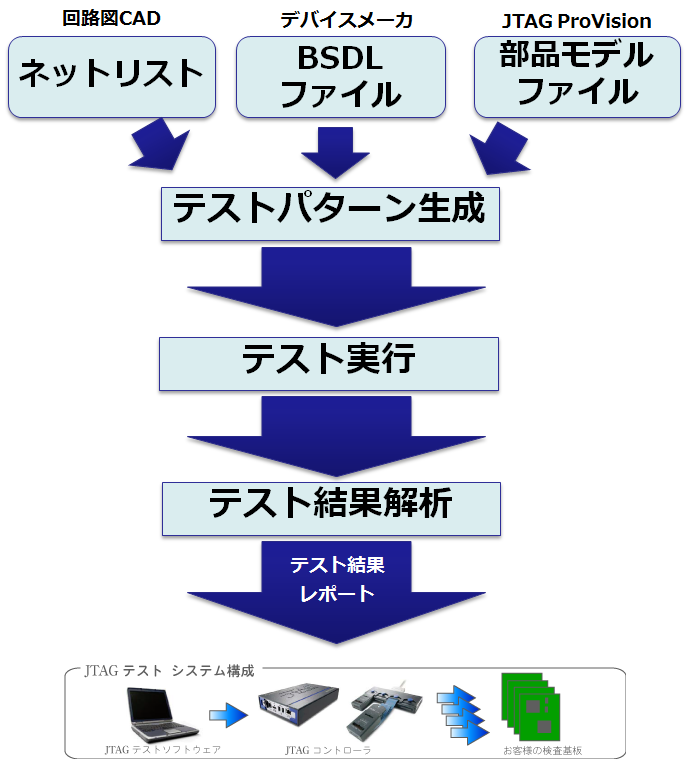

JTAGテストには何が必要?

- ネットリスト(回路図CADから生成した基板製造時のネットリスト)

- 部品表(部品の実装状況、部品のメーカ、型番が記載された部品表)

- BSDLファイル(デバイスメーカのホームページより入手可能)

- JTAGテストツール(「JTAG ProVision」にて テストコードを自動生成可能!!)

JTAGの仕組み

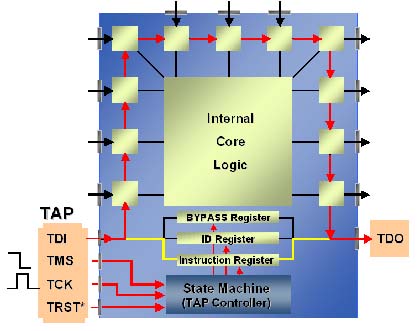

JTAGテストは、デバイス内部の本来のコア・ロジックと各ピンの間にテスト・プローブと等価な働きをするセルと呼ばれるレジスタを配置し、これを結合してシフトレジスタを構成。

このシフトレジスタを制御することによりテストデータの入力と、これに対するレスポンスによりテストを実行します。デバイス内部の境界をテストデータがスキャニングすることから、バウンダリスキャン・アーキテクチャと呼ばれます。

- JTAG TAP 信号(Test Access Port)

- TDI (Test Data Input): テストデータの入力

- TDO (Test Data Output): テストデータの出力

- TMS (Test Mode Select): JTAGの動作選択

- TCK (Test ClocK): テストクロック

- TRST (Test ReSeT): JTAG機能のリセット(※Option端子)

データレジスタには、コアロジックと入出力ピンの境界に配置されたバウンダリスキャン・レジスタ、TDIOピンからTDOピンへバイパスさせる経路であるバイパスレジスタ、およびその他のデータレジスタによって構成されます。

その他のレジスタはオプションであり、例えばデバイスの型式やデバイスメーカーを識別するためのIDCODEレジスタなどがあります。

TDIから入力されたデータがインストラクション・レジスタに格納され、デコードされた結果としてデータレジスタが選択されます。

TAP(Test Access Port)コントローラは、16種の状態を有するステートマシンであり、TMSおよびTCK信号により遷移し、データレジスタやインストラクション・レジスタおよびマルチプレクサなどを制御してJTAG機能を実現します。

JTAG-ICEとは

JTAG-ICE (In-Circuit Emulator)が誕生した背景

SoC (System on Chip)に内蔵されたプロセッサは交換ができないため、従来使われていたフルICEは利用できません。そこで、プロセッサに、ICEの機能の一部内蔵し、「JTAG」という規格を利用して、 内蔵ICE機能を利用してデバッグを行うJTAG-ICEとも呼ばれるデバッグアダプタが一般的になりました。

デバッグアダプタは、SoCやマイコンのデバッグの用途向けに作られているため、基板の実装検査には利用できませんが、本来のJTAGは、バウンダリスキャンテスト呼ばれる基板の実装検査を目的とした規格となっています。

JTAG-ICEとJTAGテストの関係

JTAG-ICEで活用されている、「JTAG」とは、5本の信号線を利用してデバッグのパケージの影響を受ける事無く、 基板全体の配線を検査するために誕生したJTAGテストの規格を利用しています。

つまり、JTAG-ICEでデバッグできるプロセッサが内蔵された殆どのデバイスでは、BGAパッケージやCSPパッケージであっても、JTAG Technologies社のテストツールを利用してハードウェアに対して、簡単にボードの実装検査ができます。

JTAGテストに対応したデバイスについて

JTAGテストに必要なBSDLファイル提供されるデバイスはJTAGテストに対応したデバイスです。

沢山のデバイスが、JTAGテストにも対応しています。

これらの他にも様々なデバイスをテストした実績がございますが、お客様との機密保持により、 掲載できる一部のデバイスだけを紹介させて頂きます。

- (株)東芝 セミコンダクター&ストレージ社 TX03

- フリースケール社 i.MX51

詳細につきましてはお役立ち情報をご参照ください

JTAGのコネクタについて

必ずJTAG-ICEやテストツールをコネクタに挿す前に、お使いになるツールのデーターシートと、接続先の基板の仕様を確認してください。

JTAG-ICEを接続するコネクタの形状や信号線の割り当ては、JTAGの規格では定められていません。

JTAGテストに対応した基板を設計される前には弊社にご相談ください。

※JTAG-ICEでは、デバッグ対象の基板をコントロールするために、JTAGの5本の信号の他に、システム全体にリセットを入れる信号なども追加されいています。

フルICEについて

フルICEは、実際プロセッサの代わりに、実装するデバッグ機能を内蔵し、 デバッグ用の信号線が繋がれた装置です。

弊社でも昔はアジレント社(その当時はHewlett-Packard社)のHP6400ワークステーションとセットで扱う、各デバイスに合わせたフルICEの開発と販売を行っていました。

現在では、プロセッサの動作周波数が非常に高く、端子の数も多く、また、SoCには、適用できないため、 現在ではJTAG-ICEのように、デバイス自身に、ICEの機能の一部を内蔵させる方式が一般的です。

お役立ち情報

JTAGテストの実績基板

JTAG技術レポート

導入事例