JTAGテクニカルニュース vol.2

今回は、JTAG/バウンダリスキャン・テストの必要性について、わかりやすくご説明します。

JTAG/バウンダリスキャン・テストの必要性

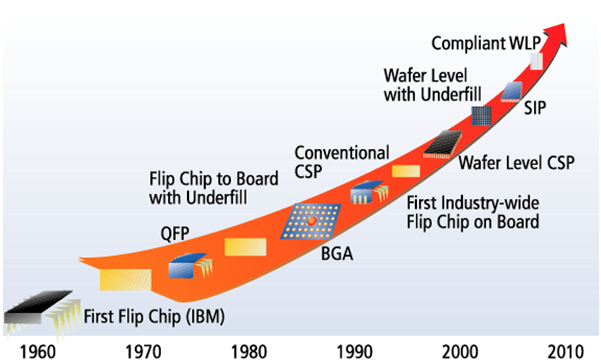

LSIパッケージ技術の変遷により、ますます高密度実装が盛んになってきた現在、従来のボード・テスト・システムでは 複雑化・高度化する組込みシステム製品の実装テストに対応できなくなってきています。

これには、いくつかの理由が挙げられます。

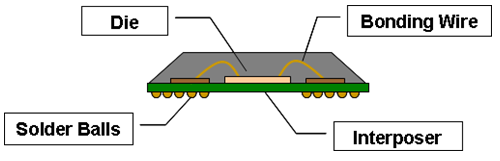

(1)BGA(Ball Grid Array)/CSP(Chip Size Package)パッケージの搭載ボードをテストするには、従来のICT(In Circuit Tester)ではプロービングが困難です。

プロービングが可能な場合でも2000ピンを超えると接触信頼性の点で実用になりません。

また、プロービングの増加により、ピン冶具(フィクスチャ)の製作コストが上がるという問題も抱えています。

さらに、高速な動作が必要とされる基板では、高速信号の品質を保持する必要があるために、信号ラインにプロービング・ポイントを配置することができません。

(2)ファンクション・テストで検査精度を上げるためには、プログラミング作成工数が増大し、多品種少量生産のボードでは採算が合いません。

また、不動作は発見できても、回路ブロック単位での判断となり、故障箇所の解析(故障箇所の特定)が困難です。

さらに、ボード上のCPUが正常に動作していない場合には、ファンクション・テスト自体を機能させることができません。

(3)BGAパッケージについては、デバイスのパッケージ下にボール状のピンが配置されているため、 AOI(Automatic Optical Inspection machine;基板外観検査装置)での故障箇所の特定は不可能です。

また、そのために、高価なX線テストシステムを導入しても、部分的な解析用であり、ボード全体および全数テストには不向きです。

また、これらのテストは電流を流したテストではないため、接続の信頼性の検査としては充分ではありません。

これら従来手法の実装検査の問題点を解決するための手法として、1990年に「IEEE Std. 1149.1」で規格化されたのが、 『JTAG/バウンダリスキャン・テスト』で、プロービング機能をデバイス内に実装することによって実現したものです。